CAMAC CDMA NORD-10 CAMAC Direct Memory Access Controller General Information

÷

# CAMAC CDMA NORD-10 CAMAC Direct Memory Access Controller General Information

Written by:

M. Collins (CERN), P. Johnsen (Un. of Oslo), R. Rausch (CERN), and T. Undheim (ND)

|                                        | REVISION RECORD   |  |  |  |  |

|----------------------------------------|-------------------|--|--|--|--|

| Revision                               | Notes             |  |  |  |  |

| 6/74                                   | Original Printing |  |  |  |  |

| •••••••••••••••••••••••••••••••••••••• |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        | 4                 |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

| ¥.                                     |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

|                                        |                   |  |  |  |  |

Publ.No. ND-12.004.01 June 1974

## TABLE OF CONTENTS

++++

| Chapters:                              |                                                                                                                                                                                                      | Page                                          |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| í                                      | IN TRODUCTION                                                                                                                                                                                        | 1-1                                           |

| 2                                      | PRINCIPLES OF OPERATION                                                                                                                                                                              | 2-1                                           |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Modes of Memory Access (CC Control Bit 2)<br>Modes of Register Access (CDMA Control Bit 2)<br>Interpretation of Q- and X-response<br>Normal Termination<br>Premature Termination<br>Special Features | 2-1<br>2-1<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3 |

| 3                                      | FRONT PANEL CONNECTORS                                                                                                                                                                               | 3-1                                           |

| 3.1<br>3.2<br>3.3                      | LINK Bus in/out<br>Trigger Inputs<br>BUSY Output                                                                                                                                                     | 3-1<br>3-1<br>3-1                             |

| 4                                      | REGISTERS                                                                                                                                                                                            | 4-1                                           |

| 4.1<br>4.2<br>4.3<br>4.4               | Word Count (WCR) Register<br>Memory Address (MAR) Register<br>CAMAC Command (NAF) Register<br>Control and Status (COST) Register                                                                     | 4-1<br>4-1<br>4-2<br>4-2                      |

| 5                                      | OTHER SIGNALS PARTLY CONTROLLED BY PROGRAM                                                                                                                                                           | 5-1                                           |

| 5.1<br>5.2                             | LAM Request<br>DMA Request Flip-Flop                                                                                                                                                                 | 5-1<br>5-1                                    |

| 6                                      | PROGRAMMING SPECIFICATIONS (SUMMARY)                                                                                                                                                                 | 6-1                                           |

| 6.1<br>6.2<br>6.3<br>6.4               | Commands Decoded<br>Other Command<br>Response<br>Control Signal                                                                                                                                      | 6-1<br>6-1<br>6-1<br>6-2                      |

| 7                                      | TIMING DIAGRAM (INTERLEAVED MODE)                                                                                                                                                                    | 7-1                                           |

| 7.1<br>7.2                             | Input to CPU<br>Output to CAMAC                                                                                                                                                                      | 7 -1<br>7 -1                                  |

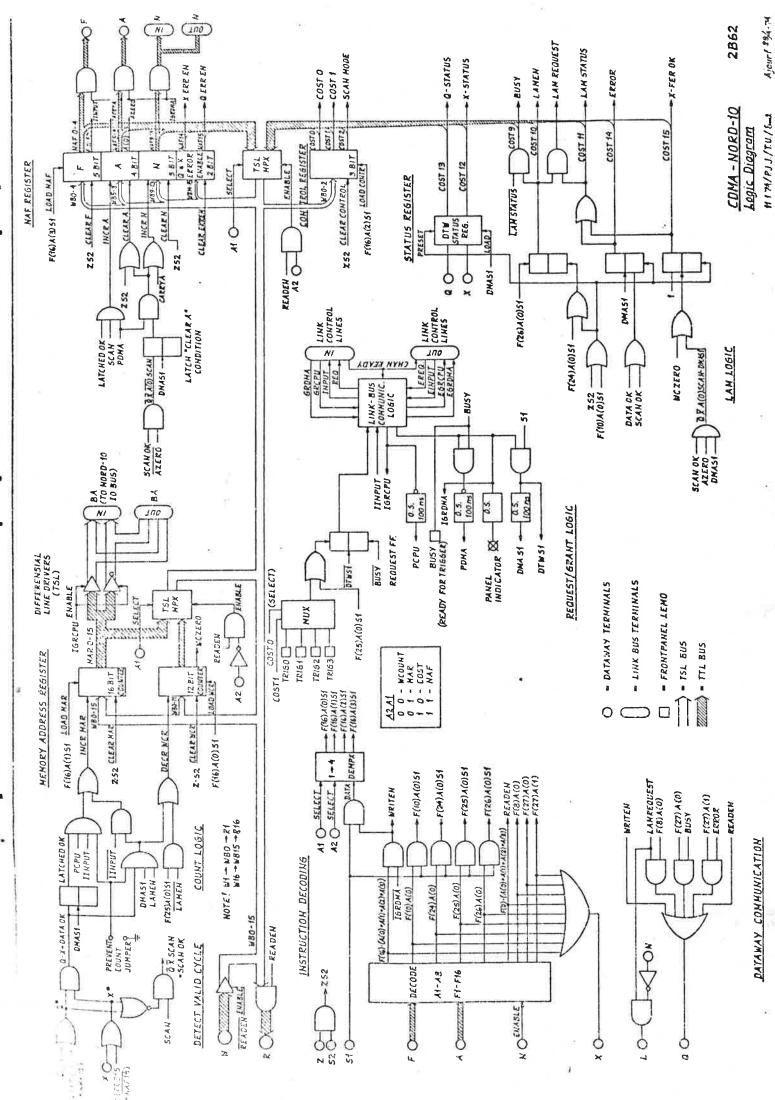

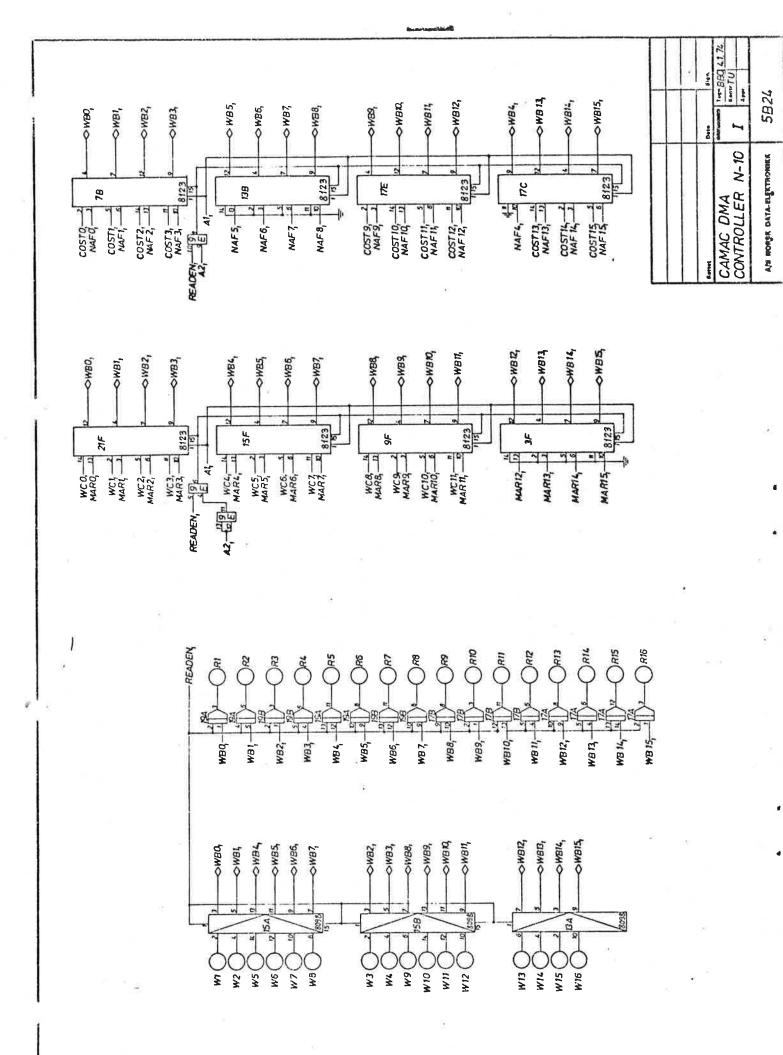

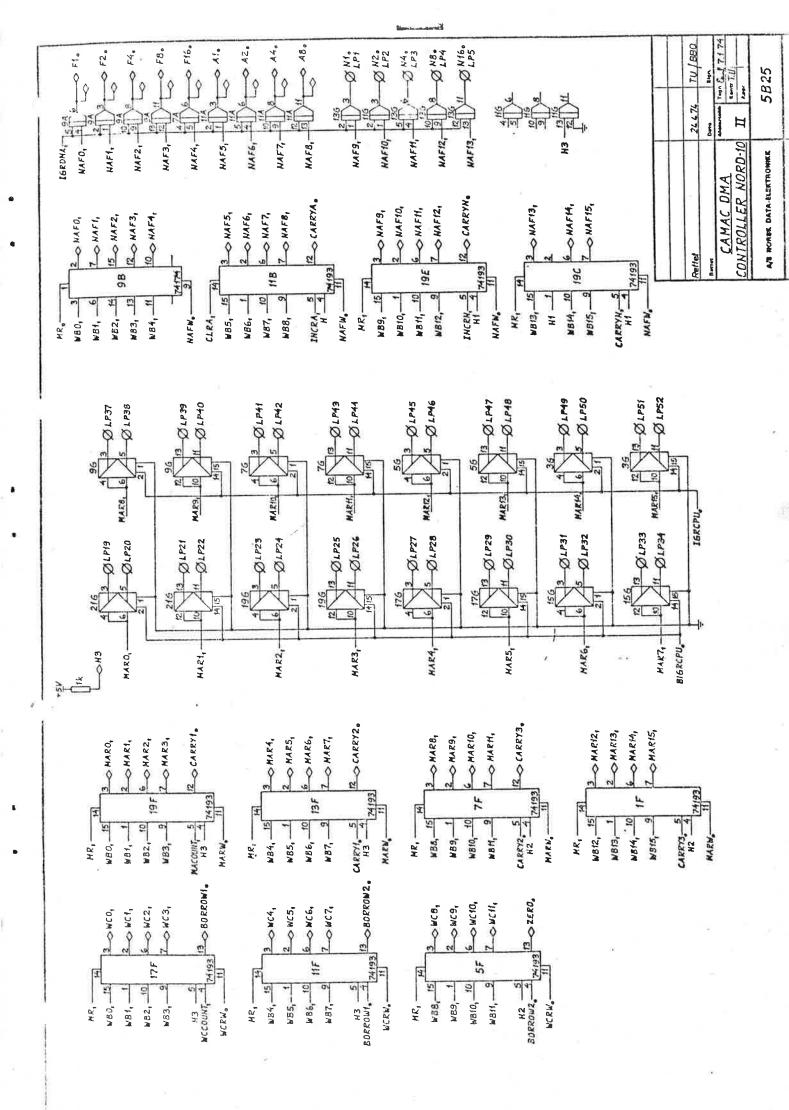

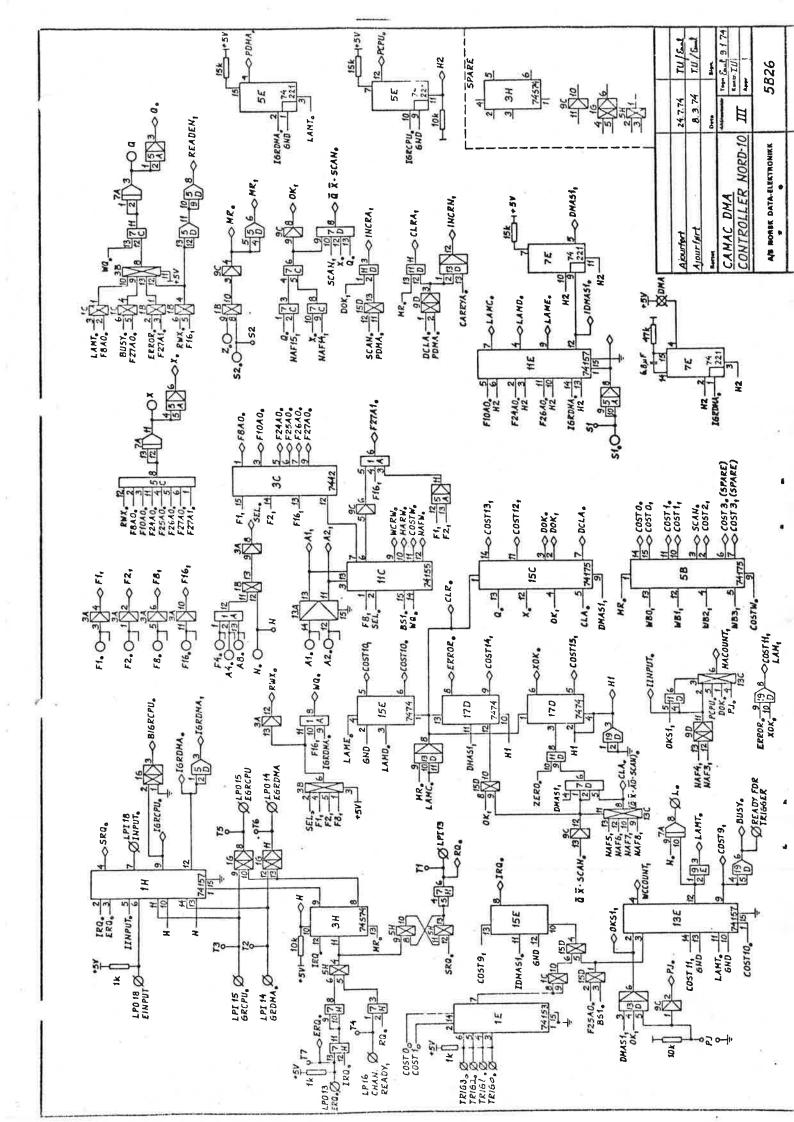

| 8                                      | LOGIC DRAWINGS                                                                                                                                                                                       | 8-1                                           |

| 8.1<br>8.2<br>8.3<br>8.4               | CDMA NORD-10 Logic Diagram<br>CAMAC DMA Controller NORD-10 - I<br>CAMAC DMA Controller NORD-10 - II<br>CAMAC DMA Controller NORD-10 - III                                                            | 8-2<br>8-3<br>8-4<br>8-5                      |

#### IN TRODUCTION

1

The Direct Memory Access Controller (CDMA) is a single width module with the necessary hardware to provide direct memory access to or from a CAMAC station.

Each CDMA can serve one CAMAC module in normal mode, or an array of modules in scan mode. Hence each module needing independent channel service it must have its private CDMA "daisy chained" to the LINK bus. The CDMA closest to the crate controller has highes priority and the furthest hase lowest priority.

The module contains:

- Memory Address register,

- Word Count register,

- NAF (CAMAC command) register,

- Control register, and

- Status register.

Furthermore it has the necessary control logic to communicate with the crate controller and other CDMA's along the LINK bus.

Channel access is requested at one of the two front panel trigger outputs. / Triggers may be due to a LAM request or from a special sequence module managing complex data transfers.

#### PRINCIPLES OF OPERATION

A channel transfer may be performed in two modes of memory access and two modes of CAMAC module register access.

The Repeat Mode described in EUR 4100, Section 5.4.3.2, is not implemented. For Address Scan Mode (Section 5.4.3.1) and Stop Mode (Section 5.4.3.3), see Section 2.2.

### Modes of Memory Access (CC control bit 2)

The channel may operate in Interleaved or Continous (Block) mode according to the CC - NORD-10 CAMAC crate controllers decision (control bit 2, set by program).

Interleaved mode is intended for single word and multiple asynchronous DMA transfer occuring at random times (Asynchronous communication between module and memory).

Continous (Block) mode is intended for fast block transfers with the Dataway cycle synchronized with the memory cycle of the CPU.

Blocks may also be transferred in Interleaved mode at an appreciable speed (about half the Continous (Block) speed).

As Interleaved transfer is asynchronous, idle Dataway and CPU time are avoided. This mode is therefore always recommended, unless very fast transfer is required.

Single word transfer in continous mode is also possible, but should be avoided as much CPU and Dataway time are vasted. This is due to the time required to prepare and terminate synchronization of the two cycles.

In Interleaved mode the CDMA loose control over the channel when one word is transferred, and must compete with higher priority controllers to retrieve it.

In Continous Block mode the same CDMA retains control of the channel untill end of block or removal of trigger (see Section 3.2) if no DMA in higher priority crates is requesting.

#### 2.2

Modes of Register Access (CDMA control bit 2)

Single Register transfer is executed according to the content of the command (NAF) register within the CDMA. The transfer terminates when the specified word count is reached.

In Address Sean mode CAMAC registers at successive subaddresses in successive stations are accessed (see Section 2.3), according to the function F of the CDMA command register which start the scan at address NA. The scan terminates at an unoccupied station or at a specified word count, whichever occurs first.

#### ND-12.004.01

2.1

2

Termination at an empty station is a safety measure, yet it may be avoided as explained in Section 2.6.

Stop mode may be considered as a premature termination of the Single Register mode (see Section 2.6).

Repeat mode is not implemented due to lack of security against system lockup, and the general uselessness of this mode except in special cases where the whole computer can be dedicated to completion of a single data transfer. Single Register transfer in Interleaved mode is a better choice in a practical real time system.

## Interpretation of Q- and X-response

Error conditions may arise, depending on the expected Q- and X-response. Errors are enabled by bit 14 and 15 of command register, identical to the convention for PIO (see Section 4.3).

In the following Q<sup>\*</sup> means (Q+ $\overline{NAF15}$ ) and X<sup>\*</sup> means (X+ $\overline{NAF14}$ ). Hence if both X and Q errors are disabled (NA14 = NAF15 = 0), Q<sup>\*</sup> and X<sup>\*</sup> will always be true.

At S1 time of a channel transfer CDMA examine  $Q^*$  and  $X^*$ , and for each word transferred, the following actions take place:

$Q^* = X^* = 1$

2.3

$Q^+ = 0, X^+ = 1$  $Q^+ = 1, X^+ = 0$

$Q^* = X^* = 0$

Data valid Increment Memory Address register. Decrement Word Count register.

In Scan mode only: If A = 15; increment A. If A = 15; clear A, increment N.

Command accepted; Data invalid or Module invalid. (Not practical.) Except for Status, all registers are

uneffected. Premature termination.

Data invalid; Command not accepted. Memory Address and Word Count unaffected.

In Single Register mode: Premature termination.

In Scan mode:

- If A = 0; clear A, increment N.

- If A = 0; normal termination.

#### 2.4 Normal Termination

At normal termination the following status bits are affected:

Since COST 10 (LAM Request enable) of necessity must be 1 (see Section 4.4) a LAM Request is also issued.

Premature Termination

2.5

2.6

In this case the status is:

| COST 15 | (X-FFR OK)              | e 0        |

|---------|-------------------------|------------|

| COST 14 | (ERROR)                 | - 1        |

| COST 11 | (LAM STATUS)            | 1          |

| COST 9  | (BUSY)                  | = <b>0</b> |

| COST 10 | · COST 11 (LAM REQUEST) | .: 1       |

Special Features

Whether the termination is normal or not, Memory Address register points to the next "unused" location, and Word Count register contains the number of words left in the block. Hence no "error holes" arise in the data buffer due to premature termination. It is thus possible to continue the transfer without modification of Word Count or Memory Address.

In order to continue, LAM must be cleared and reenabled, which sets BUSY (see Section 4.4):

Observe the possibility to implement Stop mode (EUR 4100, 5.4.3.3). Even though the Status register indicates error termination caused by Q = 0, it it easy to identify the valid data buffer by means of Memory Address register.

In Sean mode empty stations will be ignored if NAF14 = NAF15 = 0, and hence the sean will continue untill Word Count reaches zero or the N register overflows. When N overflows, missing X error is automatically enabled and will cause termination owing to missing X response from station number 0 (!). (Commands with station numbers 0 and 24-31 are dummy.)

If scanning accidently runs riot, there is no risk that the content of the CDMA will be overwritten, as writing is inhibited during DMA - Dataway cycles.

However, one CDMA may be written into when the Dataway is under the command of another CDMA. E.g. one CDMA loads NAF commands from a core table into another CDMA, which thereupon executes them.

#### FRONT PANEL CONNECTORS

To obtain communication outside the Dataway, a number of connectors are mounted on the front panel.

#### 3.1 LINK Bus in/out

3

Two CANNON 52 pins connectors are provided for entry and exit of the LINK bus. The IN connector is linked to the Crate controller or the OUT connector of the previous DMA or AFC controller.

In addition to several control signals the LINK bus furnishes the station address N to the control station (25) and the memory address to the NORD-10 I/O bus. The pin allocation is summarized in table 1.

#### 3.2 Trigger Inputs

The four (active and low) 1K pullup trigger inputs are functionally equivalent. The two least significant bits of COST register enables one of the trigger inputs when the DMA module is BUSY (B). (Binary coded).

The significance of BUSY is stated in Section 4.4 and in the following.

Triggers may be levels or pulses of minimum width 50 ns. The resulting request is stored in a flip-flop untill the trailing edge of S1 (see Logic Diagram). If the trigger is removed before this time, the flip-flop is cleared. If still present, the request is maintained, asking the computer for another cycle. Hence the decision whether it should be removed or not, should be made at latest as a response to the leading edge of S1.

When  $BUSY \rightarrow 0$  any existing request is cleared, and all triggers appearing whilst BUSY = 0 are ignored. Consequently an unprocessed trigger pulse will not be remembered for subsequent handling when BUSY = 1 reappears.

In continous (Block) mode the trigger should be present until termination of block for economy of CPU and Dataway time (see Section 2.1).

#### BUSY Output

3:3

The BUSY active low-TTL output may be utilized by trigger logic to detect termination. (READY FOR TRIGGER) (Lemo socket at front)

| Pin | Signal           | Signal Standard                            |

|-----|------------------|--------------------------------------------|

| 1   | NI               | OC-TTL                                     |

| 2   | N2               | - H -                                      |

| 3   | N4               | - <u>"</u> - <u>"</u> -                    |

| 4   | N8               | = " =: <sub>***</sub> ** <sub>2</sub> , ** |

| 5   | N16              | _ H                                        |

| 6   | GND              |                                            |

| 7   | RQAFC 1          | Not used by CDMA                           |

| 8   | GRAFC 1          | _ U * <sup>*</sup> _ * *                   |

| 9   | GND              |                                            |

| 10  | GND              |                                            |

| 11  | RQAFC 2          | Not used by CDMA                           |

| 12  | GRAFC 2          | - " -                                      |

| 13  | RQ DMA           | TTL                                        |

| 14  | GR DMA (DATAWAY) | 11                                         |

| 15  | GRCPU            | 17                                         |

| 16  | CHAN READY       | 17                                         |

| 17  | GND              | <                                          |

| 18  | INPUT            | u <sup>s</sup>                             |

| 19  | BA 0 (S)         | TSL                                        |

| 20  | BA 0 (R)         | н,                                         |

| 21  | BA 1 (S)         | H                                          |

| 22  | BA 1 (R)         |                                            |

| 23  | BA 2 (S)         | n                                          |

| 24  | BA 2 (R)         | п                                          |

| 25  | BA 3 (S)         | · · · · · · ·                              |

| 26  | • BA 3 (R)       |                                            |

| 27  | BA 4 (S)         |                                            |

| 28  | BA 4 (R)         |                                            |

| 29  | BA 5 (S)         |                                            |

| 30  | BA 5 (R)         | н                                          |

| 31  | BA 6 (S)         |                                            |

| 32  | BA 6 (R)         | "                                          |

3-2

I

1

١

1

ļ

1

ł

1

ND-12.004.01

CONT.

| Pin | Signal     | Signal Standard |

|-----|------------|-----------------|

| 33  | BA 7 (S)   | TSL             |

| 34  | BA 7 (R)   | п               |

| 35  | GND        |                 |

| 36  | Not used   | er.             |

| 37  | BA 8 (S)   | и <sup>1</sup>  |

| 38  | BA 8 (R)   | .,              |

| 39  | BA 9 (S)   | 17              |

| 40  | BA 9 (R)   |                 |

| 41  | BA 10 (S)  |                 |

| 42  | BA 10 (R)  |                 |

| 43  | 13A 11 (S) | п               |

| 44  | BA 11 (R)  | 17              |

| 45  | BA 12 (S)  |                 |

| 46  | BA 12 (R)  | e H             |

| 47  | BA 13 (S)  |                 |

| 48  | BA 13 (R)  | 11              |

| 49  | BA 14 (S)  | 11              |

| 50  | BA 14 (R)  |                 |

| 51  | BA 15 (S)  | 11              |

| 52  | BA 15 (R)  | 17              |

Table 1: Pin Allocation for LINK Bus Connectors

#### REGISTERS

The least significant bit of the registers is designated 0 to conform with the NORD-10 notation. Hence Dataway lines R1 and W1 relate to bit 0 etc.

$X^*$  and  $Q^*$  are used in the sense stated in Sections 2.3 and 4.3.

#### 4.1

4

#### Word Count (WCR) Register

This 12 bits register is initially loaded with the desired block length. It is decremented <u>after</u> each valid word transferred (see Section 2.3). Accordingly it contains the number of words left in the block at all times. Word Count 0 will cause termination of transfer.

Observe that the block length will be equal to the content of the Word Count register, and not Word Count + 1. E.g. Word Count =  $377_8$  will cause  $255_{10}$  words to be transferred.

Note that only Word Count - 0 is detected as termination. Hence a transfer starting with Word Count = 0 will be interpreted to signify a block length of  $10000_8$ .

For maintenance purposes a jumper may be inserted on the printed circuit board to prevent Word Count dccrement and Memory Address increment.

| Read      | : | <b>F</b> (0) <b>A</b> (0)                                  |

|-----------|---|------------------------------------------------------------|

| Write     | : | F(16) A(0)                                                 |

| Decrement | : | $Q^* \cdot X^* = 1$ , F(25) A(0) $\cdot \overline{COST10}$ |

| Clear     | : | Z                                                          |

If BUSY = 1, F(25) A(0) requests a cycle, and Word Count is decremented (and Memory Address incremented) only if the resulting Q and X response indicate "data valid".

#### 4.2

#### Memory Address (MAR) Register

This 16 bit register holds the memory address of the next word to be transferred to/from memory. It is incremented after each valid word of data transferred (see Section 2.3).

When preparing a transfer, the register is loaded with the start address of memory data buffer.

| Read      | :  | F(0) A(1)           |

|-----------|----|---------------------|

| Write     | :  | F(16) A(1)          |

| Increment | Ξ. | $Q^* \cdot X^* = 1$ |

| Clear     | :  | Z                   |

## 4.3 CAMAC Command (NAF) Register

The CAMAC command to be executed during a channel transfer is contained in this 16 bits register. The format is:

| Bit  | 0;              |    | F1             |

|------|-----------------|----|----------------|

| 11   | 1:              |    | F2             |

| **   | 2:              |    | F4             |

| 11   | $\frac{2}{3}$ : |    | F8             |

| 11   | 4:              |    | F16            |

| 11   | 5:              |    | Aí             |

| F.F. | $\frac{5}{6}$ : |    | A2             |

| 11   | 7:              |    | A4             |

| 11   | $\frac{8}{9}$ : |    | A8             |

| 11   | 9:              |    | N1             |

| 11   | 10:             |    | N2             |

| 11   | 11:             | 19 | N4             |

| **   | 12:             |    | N8             |

| 11   | 13:             |    | N16            |

| 11   | 14:             |    | X error enable |

| **   | 15:             |    | Q error enable |

The sense of bits is identical to that defined for Crate Controller NAF register. (CC - NORD-10.)

In Scan mode A and N are modified after each Dataway cycle according to the expected Q and X response (see Section 2.3).

Bits 14 and 15 enable error termination to occur if X or Q response is missing. I.e. error  $= \overline{Q} \cdot NAF15 + \overline{X} \cdot NAF14 = \overline{Q}^* + \overline{X}^*$ . Error = 0means "data valid". In Scan mode however,  $Q^* = X^* = 0$  has a special meaning as stated in Section 2.3.

| Read : |   | F(0) A(3)  |  |

|--------|---|------------|--|

| Write  | : | F(16) A(3) |  |

| Clear  | : | Z          |  |

In Scan mode:

| Clear A :    | $Q^* \cdot X^* \cdot \Lambda (15) = 1, \ \overline{Q}^* \cdot \overline{X}^* \cdot \overline{\Lambda} (0) = 1$ |

|--------------|----------------------------------------------------------------------------------------------------------------|

| Increment A: | $\mathbf{Q}^* \cdot \mathbf{X}^* \cdot \overline{\mathbf{\Lambda}(15)} = 1$                                    |

| Increment N: | $Q^* \cdot X^* \cdot A(15) = 1$ , $\overline{Q}^* \cdot \overline{X}^* \cdot \overline{A(0)} = 1$              |

4.4

Control and Status (COST) Register

This is a 10 bits register which governs the autonomous action of the module.

| Read  | : | (All bits) : | F(0) A(2)  |

|-------|---|--------------|------------|

| Write | : | (Bits 0-2):  | F(16) A(2) |

Set and Clear are to a certain extent controlled by program as stated in the following.

| : I                                                                | Set                                 | Clear                                           | Test       |

|--------------------------------------------------------------------|-------------------------------------|-------------------------------------------------|------------|

| Bit 0: Trig 1 enable<br>Bit 1: Trig 2 enable<br>Bit 2: Scan enable |                                     | Z<br>Z<br>Z                                     |            |

| Bit 3-8: Not used<br>Bit 9: Transfer BUSY                          | F(26) A(0) if LAM<br>status cleared | F(10) A(0),<br>F(24) A(0), Z                    |            |

| Bit 10: LAM Request<br>enable                                      | F (26) A (0)                        | F(10) A(0), Z<br>F(10) A(0), T<br>F(24) A(0), Z |            |

| Bit 11: LAM Status                                                 |                                     | F(10) A(0), Z                                   |            |

| Bit 12: Dalaway X-<br>response                                     | F(10) A(0), Z                       |                                                 |            |

| Bit 13: Dataway Q-<br>response                                     | F(10) A(0), Z                       |                                                 |            |

| Bit 14: Q+X response<br>FRROR                                      |                                     | F(10) A(0), Z                                   | F(27) A(1) |

| Bit 15: Transfer OK<br>(complete)                                  |                                     | F(10) A(0), Z                                   |            |

# Description of the individual bits:

| Bit 0: | Enables Trigg | er input 1 to set Request flip-flop |

|--------|---------------|-------------------------------------|

|        | Read :        | F (0) A (2)                         |

|        | Write :       | F (16) A (2)                        |

|        | Clear:        | Z                                   |

| Bit 1: | Enables Trigg | er input 2 to set Request flip-flop |

|        | Read :        | F (0) A (2)                         |

|        | Write :       | F(16) A(2)                          |

|        | Clear:        | Z                                   |

| Bit 2: | Enables CDMA  | A to operate in Scan mode           |

|        | Read :        | F(0) A(2)                           |

|        | Write:        | F(16) A(2)                          |

|        | Clear:        | Z                                   |

|        |               |                                     |

Indicates that CDMA is ready for channel transfer and that triggers are accepted.

| COST9 = CO | ST10.COST11                                       |

|------------|---------------------------------------------------|

| Read :     | F(0) A(2)                                         |

| Set :      | F(26) A(0)  if  COST11 = 0                        |

| Clear :    | F(10) A(0), F(24) A(0), Z, COST14 = 1, COST15 = 1 |

| Test :     | F(27) A(0); generates $Q = 1$ if $COST9 = 1$      |

Bit 10:

Enables LAM status to become a LAM request. Setting of this bit is necessary to execute a channel transfer.

Is the LAM status indicating that termination has occurred?

| Read  | : | F(0) A(2)                 |  |

|-------|---|---------------------------|--|

| Set   | : | F(26) A(0)                |  |

| Clear | : | F(10) A(0), F(24) A(0), Z |  |

Bit 11:

COSTII = COSTI4 + COSTI5

| Read :  | F(0) A(2)                |

|---------|--------------------------|

| Set :   | COST14 = 1, $COST15 = 1$ |

| Clear : | F(10) A(0), Z            |

Bit 12:

Is the X-response of the last DMA-Dataway cycle under command of this CDMA?

| Read :  | F(0) A(2)              |  |  |

|---------|------------------------|--|--|

| Write : | Status of X-line at S1 |  |  |

| Set :   | F(10) A(0), Z          |  |  |

------

Bit 13:

Is the Q-response of the last DMA-Dataway cycle under command of this CDMA?

| Read :  | F(0) A(2)              |

|---------|------------------------|

| Write : | Status of Q-line at S1 |

| Set :   | F(10) A(0), Z          |

Bit 14:

Is set if the expected Q or X response of the DMA-Dataway cycle is missing, LAM source.

| Read : | F (0) A (2)                                                              |

|--------|--------------------------------------------------------------------------|

| Set :  | $\overline{\text{COST13}}$ NAF15 1, $\overline{\text{COST12}}$ NAF14 = 1 |

| Clear: | F(10) A(0), Z .                                                          |

| Test : | F(27) A(1); generates $Q = 1$ if COST14 = 1                              |

Bit 15:

1

1

1

1

1

1

T-SAL

{: •

Ĩ

| Is set | on nor | mal termination of a transfer, LAM source.                                                                                                |  |

|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Read   |        | F(0) A(2)                                                                                                                                 |  |

| Set    | :      | Word Count $\rightarrow 0$ , COST2 $\cdot$ COST12 $\cdot$ COST13 $\cdot$ A(0) = 1<br>(A(0) = NAF5 $\cdot$ NAF6 $\cdot$ NAF7 $\cdot$ NAF9) |  |

Clear: F(10) A(0), Z

## OTHER SIGNALS PARTLY CONTROLLED BY PROGRAM

5.1 LAM Request

5

Informs the computer that termination has occurred, whether normal or premature.

LAM request = LAM status  $\cdot$  LAM request enable.

Note: As LAM request must be enabled to allow channel transfer, a LAM request is always issued at termination.

| Read :  | As part of Graded LAM status in Crate Controller |

|---------|--------------------------------------------------|

| Set :   | $COSTI0 \cdot COSTII = 1$                        |

| Clear : | F(10) A(0), F(24) A(0), Z                        |

| Test :  | F(8) A(0), generates $Q = 1$ if LAM request = 1  |

### 5.2 DMA Request Flip-Flop

It holds the request for the channel. It is primarily set by external triggers (see Section 3.2), but may be set by program for test purposes.

Set : Selected TRIGGER  $\cdot$ COST9, F(25) A(0)  $\cdot$ COST9 Clear: COST9 = 0, End of S1 if trigger is absent.

If COST10 - 0, F(25) A(0) decrements Word Count only.

|                                              | PROGRAMMING | S SPECIFICATIONS (SUMMARY)                                                                             |  |  |

|----------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------|--|--|

|                                              | Commands d  | lecoded                                                                                                |  |  |

|                                              | F(0) A(0) : | READ WCR                                                                                               |  |  |

|                                              | F(0) A(1) : | READ MAR                                                                                               |  |  |

|                                              | F(0) A(2) : | READ COST                                                                                              |  |  |

|                                              | F(0) A(3) : | READ NAF                                                                                               |  |  |

|                                              | F(8) A(0) : | TEST LAM REQUEST, $Q = 1$ IF SET                                                                       |  |  |

|                                              | F(10) A(0): | CLEAR LAM STATUS, ERROR STATUS, TRANSFER OK<br>STATUS<br>DISABLE LAM REQUEST<br>SET Q STATUS, X STATUS |  |  |

|                                              | F(16) A(0): | WRITE WCR                                                                                              |  |  |

|                                              | F(16) A(1): | WRITE MAR NOTE! WRITING IS NOT EXECUTED                                                                |  |  |

|                                              | F(16) A(2): | WRITE COST<br>IF COMMAND IS DUR TO INTERNAL<br>NAF REGISTER                                            |  |  |

|                                              | F(16) A(3): | WRITE NAF                                                                                              |  |  |

|                                              | F(24) A(0): | DISABLE LAM REQUEST                                                                                    |  |  |

|                                              | F(25) A(0): | REQUEST DMA CYCLE IF DMA BUSY.<br>DECREMENT WORD COUNT IF LAM DISABLED                                 |  |  |

|                                              | F(26) A(0): | ENABLE LAM REQUEST                                                                                     |  |  |

| F(27) A(0): TEST BUSY STATUS, $Q = 1$ IF SET |             |                                                                                                        |  |  |

|                                              | F(27) A(1): | TEST ERROR STATUS, $Q = 1$ IF SET                                                                      |  |  |

|                                              | Other Comm  | and                                                                                                    |  |  |

|                                              | Z :         | CLEAR WCR, MAR, NAF, COST EXCEPT BITS 12-13<br>SET COST BITS 12-13                                     |  |  |

6 - 1

6.3 Response

6.2

6

6.1

X : TO ALL DECODED FUNCTIONS Q : TO ALL READ FUNCTIONS TO ALL WRITE FUNCTIONS PROVIDED THE COMMAND IS NOT DUE TO INTERNAL NAF REGISTER TO TEST FUNCTIONS F(8) A (0), F(27) A (0) AND F(27) A (1)

## 6.4 Control Signal

L : RAISED ON NORMAL OR PREMATURE TERMINATION

Warning

IF TRANSFER IS STARTED WITH WORD COUNT = 0, THE BLOCK LENGTH IS TAKEN TO BE  $4096_{10}$ .

7

TIMING DIAGRAM (INTERLEAVED MODE)

7.1

Input to CPU

|                                |       |                     |            | the second se |                                          |

|--------------------------------|-------|---------------------|------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------|

| TRIGGER                        | ЪĽ    |                     |            |                                                                                                                 |                                          |

| RQ DMA                         | 4     |                     |            |                                                                                                                 |                                          |

| GR DMA (DATAWAY)               |       |                     |            |                                                                                                                 |                                          |

| S1, S2                         |       |                     | −Ļ₽Ĺ       |                                                                                                                 | 2011 - (12010) - Alfaber (180)           |

| DMAS1 (DECR WCR)               |       |                     | -45-       |                                                                                                                 |                                          |

| WCZERO                         |       |                     | 5          |                                                                                                                 |                                          |

| BUSY                           |       | i particular de tra | <u>`</u> ` |                                                                                                                 |                                          |

| PDMA (MODIFY NAF)              |       |                     |            |                                                                                                                 |                                          |

| RQ CPU (FROM CC)               | ÷     | (e)                 |            | 4                                                                                                               |                                          |

| GR CPU                         |       |                     |            | 2                                                                                                               |                                          |

| PCPU (INCR MAR)                |       |                     |            |                                                                                                                 |                                          |

| 7.2 Output to                  | CAMAC |                     |            |                                                                                                                 |                                          |

| TRIGGER                        |       |                     |            |                                                                                                                 |                                          |

| RQ DMA                         | —Ъ_   |                     |            |                                                                                                                 |                                          |

| RQ CPU (FROM CC)               | -4_   |                     |            |                                                                                                                 | na an a |

| GR CPU                         |       |                     |            | <u></u>                                                                                                         |                                          |

| DATA READY (TO CC)             |       |                     | }          |                                                                                                                 |                                          |

| GR DMA (DATAWAY)               | 5.2   |                     |            |                                                                                                                 |                                          |

| S1, S2                         |       |                     |            | Y_r                                                                                                             |                                          |

| DMAS1 (DECR WCR &<br>INCR MAR) |       |                     |            | - es                                                                                                            |                                          |

| WCZERO                         |       |                     |            | 5                                                                                                               |                                          |

| BUSY                           |       |                     |            | <u> </u>                                                                                                        |                                          |

| PDMA (MODIFY NAF)              |       |                     |            | ana ana ina mana ina 2007.                                                                                      | - Y                                      |

ND-12.004.01

7-1

LOGIC DRAWINGS

8